- 您现在的位置:买卖IC网 > Sheet目录1993 > DS1337S+C01 (Maxim Integrated Products)IC RTC SERIAL 2WIRE LP 8-SOIC

DS1337 I

2C Serial Real-Time Clock

HANDLING, PC BOARD LAYOUT, AND ASSEMBLY

The DS1337C package contains a quartz tuning-fork crystal. Pick-and-place equipment may be used, but

precautions should be taken to ensure that excessive shocks are avoided. Ultrasonic cleaning should be avoided

to prevent damage to the crystal.

Avoid running signal traces under the package, unless a ground plane is placed between the package and the

signal line. All N.C. (no connect) pins must be connected to ground.

Moisture-sensitive packages are shipped from the factory dry-packed. Handling instructions listed on the package

label must be followed to prevent damage during reflow. Refer to the IPC/JEDEC J-STD-020 standard for

moisture-sensitive device (MSD) classifications.

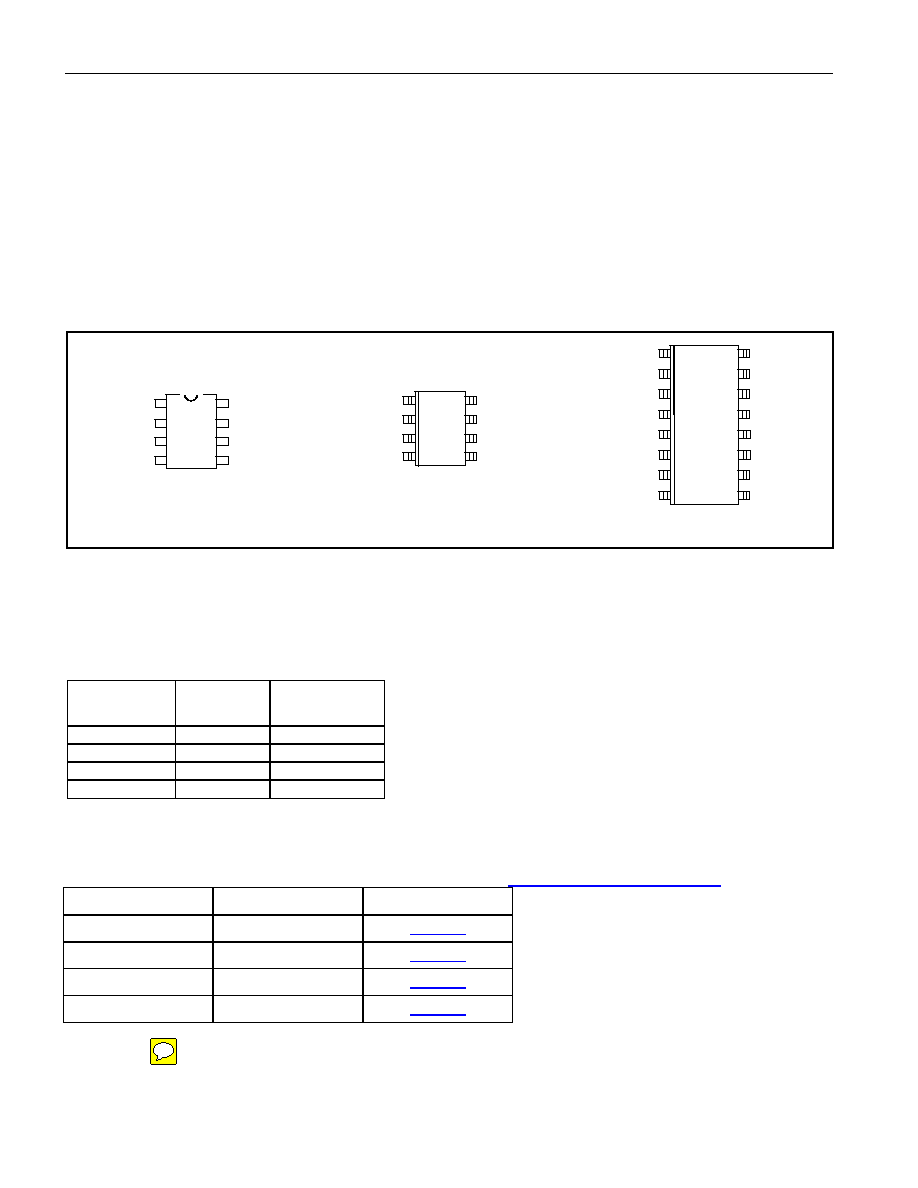

PIN CONFIGURATIONS

TOP VIEW

SCL

SDA

DS1337C

SQW/

INTB

GND

CHIP INFORMATION

TRANSISTOR COUNT: 10,950

PROCESS: CMOS

THERMAL INFORMATION

PACKAGE

THETA-JA

(°C/W)

THETA-JC

(°C/W)

8 DIP

110

40

8 SO

170

40

8 μSOP

229

39

16 SO

73

23

PACKAGE INFORMATION

For the latest package outline information and land patterns, go to

PACKAGE TYPE

PACKAGE CODE

DOCUMENT NO.

8 PDIP

P8+8

8 SO

S8+2

21-0041

8

MAX

U8+1

16 SO

W16-H2

DIP

INTA

VCC

INTA

VCC

X1

VCC

X1

N.C.

DS1337

N.C.

SQW

/INTB

X2

SQW

/INTB

X2

DS1337

N.C.

SCL

INTA

SCL

N.C.

SDA

GND

SDA

GND

N.C.

SO, SOP

N.C.

SO (300 mils)

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

DS1338C-33#T&R

IC RTC 56BYTE NV SRAM 16SOIC

DS1339AU+

IC RTC I2C W/ALARM 8USOP

DS1339C-2#

IC RTC I2C W/ALARM 16-SOIC

DS1340Z-33/T&R

IC RTC I2C W/CHARGER 3.3V 8-SOIC

DS1340Z-3

IC RTC I2C W/CHARGER 3V 8-SOIC

DS1341T+

IC RTC I2C W/ALARM 6TDFN-EP

DS1344D-33+

IC RTC SPI 3.3V 14TDFN-EP

DS1347T+

IC RTC/CALENDAR SPI 8TDFN

相关代理商/技术参数

DS1337S+T&R

制造商:Maxim Integrated Products 功能描述:REAL TIME CLOCK SERL 8SOIC - Tape and Reel 制造商:Maxim Integrated Products 功能描述:SERIAL RTC 8P SOIC TRL LEADFREE 制造商:Maxim Integrated Products 功能描述:IC RTC SERIAL 2WIRE LP 8-SOIC 制造商:Maxim Integrated Products 功能描述:Real Time Clock I2C Serial RTC 制造商:Maxim Integrated Products 功能描述:Real Time Clock Serial SOIC8

DS1337S+T&R

功能描述:实时时钟 I2C Serial RTC RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1337U

功能描述:实时时钟 I2C Serial RTC RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1337U/T&R

制造商:Maxim Integrated Products 功能描述:REAL TIME CLOCK SERL 8USOP - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC RTC SERIAL 2WIRE LP 8-USOP 制造商:Maxim Integrated Products 功能描述:Real Time Clock I2C Serial RTC

DS1337U/T&R

功能描述:实时时钟 I2C Serial RTC RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1337U+

功能描述:实时时钟 I2C Serial RTC RoHS:否 制造商:Microchip Technology 功能:Clock, Calendar. Alarm RTC 总线接口:I2C 日期格式:DW:DM:M:Y 时间格式:HH:MM:SS RTC 存储容量:64 B 电源电压-最大:5.5 V 电源电压-最小:1.8 V 最大工作温度:+ 85 C 最小工作温度: 安装风格:Through Hole 封装 / 箱体:PDIP-8 封装:Tube

DS1337U+

制造商:Maxim Integrated Products 功能描述:SEMICONDUCTOR ((NW))

DS1337U+T&R

制造商:Maxim Integrated Products 功能描述:SERIAL RTC 8PIN USOP TRL LEADFREE 制造商:Maxim Integrated Products 功能描述:REAL TIME CLOCK SERL 8USOP - Tape and Reel 制造商:Maxim Integrated Products 功能描述:IC RTC SERIAL 2WIRE LP 8-USOP 制造商:Maxim Integrated Products 功能描述:Real Time Clock I2C Serial RTC